你真正的了解什么是振蕩器嗎?

像石英晶體振蕩器,陶瓷晶振,聲表面濾波器這些產品一樣,晶體振蕩器也是有它自身所自帶的一些參數,在上PCBA板,電路板,調試板上,都需要對應相關參數,才可以使用.尤其是一些比較高端產品應用,一定是要認準資料,并且一分一毫都不能有差的那種.差分晶體振蕩器,時鐘振蕩器,實時時鐘,恒溫晶體這些產品相對來說產品要求相對的比較高一些,工程師在選型的時候就一定會特別注意所對應的參數要求,那么在工程師或者技術指導師的面前來說什么樣的相關參數會如此重要呢??

標稱頻率:晶體振蕩器的中心或標稱輸出頻率。

封裝:石英晶體振蕩器采用各種類型的封裝,從引腳孔到表面貼裝類型。各種尺寸和功能適用于不同的應用。

頻率容差:在室溫下以百萬分率(ppm)表示的與標稱頻率的偏差。(25°±5°C)

頻率范圍:可提供振蕩器類型或型號的頻段。

頻率穩定性:與溫度窗口25°C時的測量頻率相比,即0°C至+ 70°C時的最大允許頻率偏差。典型穩定性為±0.01%(±100 ppm)。

工作溫度:輸出頻率和其他電氣,環境特性符合規范的溫度范圍。

老化:一段時間內的相對頻率變化。這種頻率變化率通常是指數性的。通常,老化在1年內最大為±5 ppm。

存儲溫度:安裝設備的溫度范圍(未施加電源電壓),不會損壞或改變設備的性能。

頻率與電源的變化:當電源電壓在規定范圍內變化時允許的最大頻率變化(Vcc典型值±10%或±5%變化)。

電源電壓(Vdd max):可以安全施加到Vcc端子的最大電壓。TTL的最大電源電壓為5.5V,HCMOS的最大電源電壓為6V。

輸入電壓(VIN):可安全施加到振蕩器輸入端的最大電壓。

輸出高電壓(VOH):在適當負載下振蕩器輸出端的最小電壓。

輸出低電壓(VOL):正確加載時振蕩器輸出的最大電壓。

電源電流(Icc):流入Vcc端子的電流相對于地。無負載測量典型電源電流。

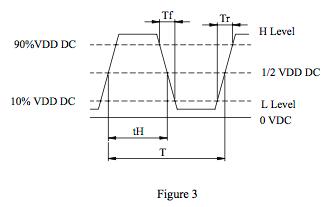

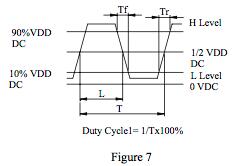

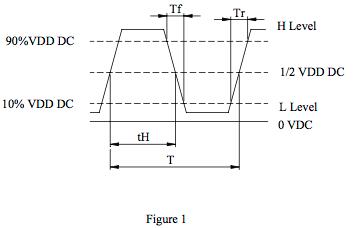

對稱性或占空比:輸出波形的對稱性形成于指定的水平(TTL為1.4V,HCMOS為1 / 2Vcc,ECL為1/2波形峰值水平)。

SYM = TH / T×100(%); 見圖1。

上升時間(Tr):從低電平到高電平轉換的波形上升時間,在指定電平下測量(HCMOS,ECL為20%至80%,TTL為0.4V至2.4V)。

下降時間(Tf):在指定級別測量的波形下降時間從高轉變為低轉換(HCMOS,ECL為80%至20%,TTL為2.4V至0.4V)。

扇出:振蕩器驅動能力的度量,表示為可由單個輸出驅動的輸入數量。它可以用等效負載電容(CL)或由二極管,負載電阻和電容組成的TTL負載電路來表示。

抖動:振蕩器輸出的相位或頻率調制。

HCMOS / TTL兼容:振蕩器采用ACMOS邏輯設計,具有TTL和HCMOS負載的驅動能力,同時保持HCMOS的最小邏輯高電平。

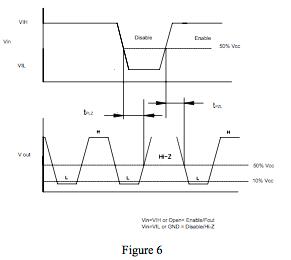

三態使能:當輸入保持OPEN或連接到邏輯“l”時,發生正常振蕩。當輸入接地(連接到邏輯“0”)時,輸出處于HIGH IMPEDANCE狀態。輸入端有一個內部上拉電阻,允許輸入保持開路。

輸出邏輯:振蕩器的輸出設計用于滿足各種指定邏輯,例如TTL,HCMOS,ECL,正弦波,限幅正弦波(DC截止)。

諧波失真:由與目標信號頻率相關的不需要的諧波頻譜分量引起的非線性失真。每個諧波分量是電功率與期望信號輸出電功率之比,并且以dBc表示,即-20dBc。當需要干凈且失真較小的信號時,諧波失真規范在正弦輸出中尤為重要。

相位噪聲:衡量振蕩器的短期頻率波動。它通常被指定為在距離載波的指定偏移頻率處的1Hz帶寬中的單邊帶(SSB)功率密度。它以dBc / Hz為單位。

待機:暫時關閉振蕩器和其他分頻器以節省功率的功能。邏輯“0”將啟用待機模式。待機模式下的禁用電流從幾微安到幾十微安不等(典型值為5pA)。由于振蕩停止,在輸出穩定之前最多有10 ms(相同的啟動時間)。

VCXO技術術語

控制電壓(Vc):施加到VCXO輸入的外部電壓。通過改變電壓,頻率相應地變化。

典型的Vc為0 VDC至5 VDC,0.5 VDC至4.5 VDC,以及0.15 VDC至3.15 VDC。

偏差或頻率可牽引性:輸出頻率相對于控制電壓變化的最小變化。單位以ppm為單位。標準可牽引力最小為±50 ppm或最小為±100 ppm。

最大可牽引性:最大控制電壓允許的最大頻率變化(正向傳遞函數)。以ppm為單位測量。

傳遞函數:頻率變化方向與控制電壓變化的關系。如果在增加控制電壓時頻率上升,則稱轉移是正的。如果頻率在增加Vc時下降,則傳遞函數為負。

輸入阻抗: VCXO網絡輸入端口與電壓控制源之間的隔離度量。典型輸入阻抗> 10KHz時> 50kohms。

線性度:與頻率與控制電壓曲線的最佳直線斜率的偏差。典型線性度為±20%或±10%。

調制帶寬:相對于1KHz輸入調制頻率的最小±3dB帶寬頻率。

中心頻率或標稱頻率:用戶指定的中心控制電壓頻率。中心頻率的標準控制電壓為VVD = 5 VDC時為2.5 VDC,Vcc = 3.3 VDC時為1.65 VDC。

振蕩器應用說明

振蕩器是產生連續輸出信號的電路; 因此它被稱為信號發生器。當產生的信號是恒定幅度和頻率的正弦波時,振蕩器電路稱為正弦波發生器。振蕩器可以在數字邏輯系列中產生方波信號,例如TTL,CMOS或ECL / PECL。

振蕩器可以分為三個明確的部分:

(1)放大器

(2)反饋連接

(3)頻率確定部件。

振蕩的要求

如果電路由兩個最低要求組成,則電路將振蕩:

(1)正反饋

(2)環路增益大于1

當我們將放大器的輸出連接到其輸入時,提供反饋。如果反饋的輸出與輸入“異相”,則電路具有負反饋(NFB)。如果輸出的反饋與輸入同相,則電路具有正反饋(PFB)。

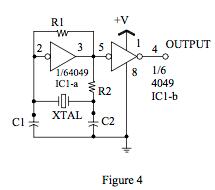

PIERCE振蕩器電路

優點:

(1)在串聯諧振處或附近運行(距離Fs約5ppm至200ppm)。(2)短期穩定性非常好。

(3)在1 kHz至200 MHz的任何頻率下工作。

(4)電路提供大輸出信號。

(5)以低功率驅動晶體。

(6)振蕩頻率對串聯

電阻或并聯電容的微小變化幾乎不敏感。

電路配置:

•在大多數皮爾斯電路中,放大器僅由一個晶體管組成。輸出可以緩沖以提供數字邏輯兼容輸出(TTL或HC-CMOS

•Pierce放大器可以設計為CMOS,TTL和ECL中的數字邏輯元件;低頻CMOS,中頻TTL和ECL對于高頻率。

晶體振蕩器中的三態控制

大多數數字系統使用由兩個狀態級別0和1表示的二進制數系統。在某些特殊應用中,需要第三狀態(Hi阻抗輸出)。TTL,HCMOS或HCMOS晶體振蕩器提供三態輸出或三態啟用/禁用功能。其常見應用包括自動測試,總線布線數據傳輸。

這三種狀態是低,高和高阻抗(Hi Z或浮動)。高阻抗狀態的輸出表現得好像它與電路斷開,除了可能有小的漏電流。三態器件具有使能/禁止輸入,通常在幾乎任何封裝的引腳1上。當使能為高電平或懸空時,器件振蕩(輸出高電平和低電平),當引腳1接地(邏輯“0”)時,器件進入高阻態。

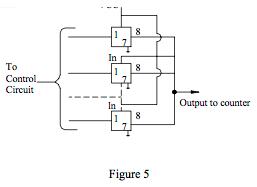

總線是一組通用的線路,通常用于數據傳輸。三態總線有幾個三態輸出連接在一起。通過控制電路,總線上的所有設備(除了一個)都具有高阻抗狀態的輸出。其余器件使能,驅動高低輸出總線。

三態功能的其他應用是用于自動測試設備(ATE)。幾個振蕩器的輸出連接在一起。對于控制電路,所有振蕩器都有一個處于高阻態的輸出。選擇的唯一振蕩器將從計數器讀出其頻率。(圖5)

在三態函數生效之前總會有一些延遲。在兩個轉換(禁用和啟用時)都會發生此效果。從低電平開始的三態輸出禁止時間是tPLZ,三態到低電平的輸出使能時間是tPZL。(圖6)

CMOS

上升和下降時間CMOS技術的上升和下降時間取決于其速度(CMOS,HCMOS,ACMOS,BICMOS),電源電壓,負載電容和負載配置。CMOS 40000系列的典型上升和下降時間為30ns,HCMOS為6ns,而ACMOS(HCMOS,TTL兼容)的最大上升和下降時間為3 ns。典型的上升和下降時間在其波形水平的10%至90%之間測量。(見圖7)

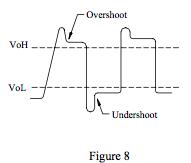

ACMOS輸出終止技術

由于ACMOS(HCMOS / TTL兼容)器件的快速轉換時間,在測試或測量電氣性能特性時必須使用正確的端接技術。端接通常用于解決電壓反射問題,這實質上導致時鐘波形中的步驟以及過沖和下沖。這可能導致錯誤的數據時鐘,以及更高的EMI和系統噪聲。

由于PC板上的跡線長度及其負載配置,還需要端接。有三種終止時鐘軌跡的通用方法,即將器件的輸出阻抗與線路阻抗相匹配的過程:

方法1:串聯終端(圖9)在串聯終端中,阻尼電阻靠近時鐘信號源放置。Rs的值必須滿足以下要求:Rs≥ZT - Ro

方法2:上拉/下拉電阻(圖10)在上拉/下拉終端中,組合的戴維寧等效于跡線的特征阻抗。這可能是最干凈的,并且不會產生反射,也會降低EMI。RT~ZT

相關資訊

- [2024-05-22]Statek低頻振蕩器CXOLP4SNSM4-8...

- [2024-03-08]32.768KHz振蕩器比普通音叉晶振...

- [2023-10-19]美國ITTI晶振發表對石英晶體和振...

- [2023-10-19]ITTI晶振揭秘CRYSTAL DEVELOPME...

- [2023-10-17]ITTIA晶振是石英行業令人興奮的...

- [2023-09-28]Crystek最新的CVCO33BE-2352-24...

- [2023-09-26]領先全球的Hosonic晶振品牌介紹...

- [2023-09-23]遙遙領先的思佳訊電子采用第四代...

.jpg)