關(guān)于皮爾斯振蕩器的了解你知道多少?

來源:http://www.sqlianchuang.cn 作者:泰河電子晶振 2019年05月05

Today, the majority of electronic circuits (including microprocessors, microcontrollers,FPGAs, and CPLDs) are based on clocked logic, requiring a timing source. Depending on the frequency accuracy requirements, some employ oscillators while others use off-the-shelf quartz crystals in conjunction with the builtin oscillator circuit embedded in most microcontrollers and microprocessors.

Most if not all embedded solutions use the Pierce oscillator configuration,integrated as part of the SoC (systemon-chip). The obvious advantages include cost, size, and power compared to a standalone oscillator. The key limitation is the proper matching of the quartz crystal with the on-board Pierce oscillator.

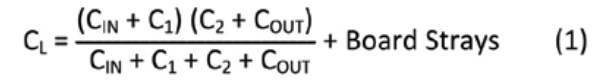

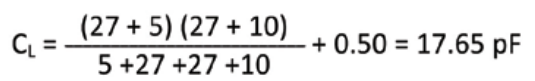

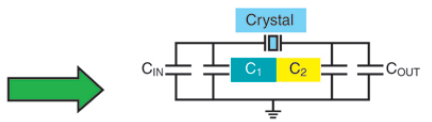

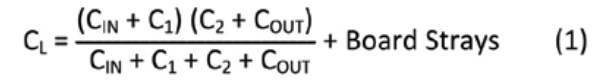

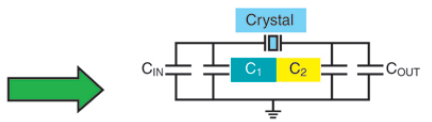

Figure 1 outlines the oscillator block and the key components that influence the overall performance of the timing loop. Let the effective load capacitance, as seen by the crystal, be CL.

如今,大多數(shù)電子電路(包括微處理器,微控制器,FPGA和CPLD)都基于時(shí)鐘邏輯,需要定時(shí)源. 根據(jù)頻率精度要求,一些采用振蕩器,而另一些采用現(xiàn)成的石英晶體與嵌入大多數(shù)微控制器和微處理器的內(nèi)置振蕩器電路相結(jié)合.

大多數(shù)(如果不是全部)嵌入式解決方案都使用皮爾斯振蕩器配置,作為SoC(systemon-chip)的一部分集成. 與獨(dú)立振蕩器相比,明顯的優(yōu)勢(shì)包括成本,尺寸和功耗. 關(guān)鍵的限制是石英晶振與板載皮爾斯振蕩器的正確匹配.

圖1概述了振蕩器模塊和影響定時(shí)環(huán)路整體性能的關(guān)鍵組件. 讓晶體看到的有效負(fù)載電容為CL.

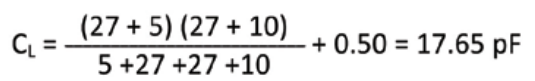

For example, let C1 = C2 = 27 pF; CIN = 5.0 pF and COUT = 10.0 pF and Board Strays = 0.50 pF.

例如,設(shè)C1 = C2 = 27 pF; CIN = 5.0pF,COUT = 10.0pF,板間距= 0.50pF.

Therefore specifying a crystal with 18.0 pF plating load capacitance would be the closest match for frequency accuracy. The selected capacitors primarily influence the overall oscillator loop capacitance, as seen by the crystal. This effective loop capacitance (CL from Eq. 1) determines how far the oscillator loop is resonating, relative to the desired resonant frequency. However, the overall longterm performance of the oscillator loop is influenced by the following factors:

因此,指定具有18.0 pF電鍍負(fù)載電容的晶體將是頻率精度最接近的匹配. 所選擇的電容主要影響整個(gè)振蕩器環(huán)路電容,如晶體所示. 該有效環(huán)路電容(來自等式1的CL)確定振蕩器環(huán)路相對(duì)于所需諧振頻率諧振的程度. 但是,振蕩器環(huán)路的整體長期性能受以下因素影響:

• The reactive impedance (Xc) of these loop capacitors.

• The inverter amplifier’s transconductance (gm).

• The presence or absence of the current limiting resistor (Rs).

• The presence or absence of the automatic gain control (AGC) or automatic level control (ALC); with-in the integrated oscillator circuit.

These factors collectively set the boundary condition of the design. This boundary condition, commonly referred to as the safety factor (SF), is an important parameter to ensure that the product design has sufficient margin to accommodate part-to-part and lot-to-lot variations; as well as, eliminating product performance uncertainty in production volume. Historically, design engineers have optimized their circuit performance via trial and error, at the expense of sig.

•這些環(huán)路電容器的無功阻抗(Xc).

•逆變器放大器的跨導(dǎo)(gm).

•是否存在限流電阻(Rs).

•是否存在自動(dòng)增益控制(AGC)或自動(dòng)電平控制(ALC); 與集成振蕩器電路配合使用.

這些因素共同設(shè)定了設(shè)計(jì)的邊界條件. 這種邊界條件,通常稱為安全系數(shù)(SF),是確保產(chǎn)品設(shè)計(jì)具有足夠的余量以適應(yīng)零件到零件和批次間差異的重要參數(shù); 以及消除產(chǎn)品性能不確定性的產(chǎn)量. 從歷史上看,設(shè)計(jì)工程師通過試驗(yàn)和錯(cuò)誤優(yōu)化了電路性能,但犧牲了信號(hào).

Fig. 1: The oscillator block and the key components that influence the overall performance of the timing loop.

圖1:振蕩器模塊和影響定時(shí)環(huán)路整體性能的關(guān)鍵部件.

nificant investment in time. Further, to properly determine the oscillator loop dynamics, the most accurate determination is made by breaking the oscillator loop and conducting key measurements using specialized equipment such as a current probe.

及時(shí)投入.此外,為了正確地確定振蕩器環(huán)路動(dòng)態(tài),通過使用諸如電流探頭的專用設(shè)備斷開振蕩器環(huán)路并進(jìn)行關(guān)鍵測(cè)量來進(jìn)行最準(zhǔn)確的確定.

Lastly, these measurements become increasingly sensitive if the timing loop is driven by a tuning-fork (32.768- kHz) crystal. These crystals are extremely sensitive to loading effects and to accurately determine the in-circuit behavior of these components, extreme care and accuracy is essential. For instance, Automotive, medical and consumer electronics solutions typically use tuning fork crystals for their real-time-clocking (RTC) needs. If the selected SOP has limited gain margin, there is a high probability that some percentage of these crystals will not properly start under adverse conditions, such as cold operating temperature (–40°C).

最后,如果定時(shí)環(huán)由音叉(32.768-kHz)晶體驅(qū)動(dòng),則這些測(cè)量變得越來越敏感.這些晶體對(duì)負(fù)載效應(yīng)非常敏感,并且準(zhǔn)確地確定這些元件的在線行為,極其謹(jǐn)慎和準(zhǔn)確性至關(guān)重要.例如,汽車,醫(yī)療和消費(fèi)電子解決方案通常使用音叉晶體來滿足其實(shí)時(shí)時(shí)鐘(RTC)需求.如果所選擇的SOP具有有限的增益裕度,則很可能這些晶體中的某些百分比在不利條件下(例如冷工作溫度(-40℃))不能正常啟動(dòng).

Another example would be a product designed to address the ZigBee related solutions, which typically has a hard boundary condition of ±40 ppm relative to the carrier, for proper operation. This ±40-ppm operational window actually needs to account for

另一個(gè)例子是設(shè)計(jì)用于解決ZigBee相關(guān)解決方案的產(chǎn)品,該解決方案通常具有相對(duì)于載波±40ppm的硬邊界條件,以實(shí)現(xiàn)正確操作.這個(gè)±40 ppm的操作窗口實(shí)際上需要考慮

• Quartz crystal set tolerance.

• Shift through reflow.

• Stability over temperature.

• Aging during product-life-cycle (such as 5 years).

• Frequency pushing and pulling.

If the oscillator loop is not optimized, most of the ±40 ppm can be potentially consumed by the set tolerance of the quartz crystal alone, thereby causing potential field failures.

•石英晶體設(shè)置公差.

•通過回流轉(zhuǎn)換.

•溫度穩(wěn)定性.

•產(chǎn)品生命周期中的老化(例如5年).

•頻率推拉.

如果振蕩器環(huán)路未經(jīng)優(yōu)化,則單獨(dú)使用石英晶體的設(shè)定公差可能會(huì)消耗大部分±40 ppm,從而導(dǎo)致潛在的現(xiàn)場(chǎng)故障.

These frequency domain failures could be primarily attributed to the oscillator frequency drifting over temperature or long-term aging, to the point that the oscillator loop is no longer within the allocated ±40-ppm operational window. Besides the issues related to oscillator-loop accuracy in the frequency domain, the oscillator-loop drive level must also be properly quantified to ensure acceptable product performance over temperature and time. For instance, a typical 24-MHz SMT quartz crystal has a drive level specification of 100 µW max. If the quartz crystal is consistently being driven at some multiple of this limit, such as 200 µW; it is possible that, over temperature or time, the oscillator circuit might start to resonate permanently or intermittently — at a spurious or overtone mode of the quartz crystal. Although relatively low on the checklist of design engineers, the Pierce oscillator driven by an external resonator — such as a quartz crystal — can present a significant challenge during a typical product launch. Characterizing the oscillator loop during the design phase should be a priority to mitigate the risk during product launch as well as field returns down the road.

這些頻域故障主要?dú)w因于振蕩器頻率隨溫度漂移或長期老化,導(dǎo)致振蕩器環(huán)路不再在分配的±40 ppm操作窗口內(nèi).除了與頻域振蕩器環(huán)路精度相關(guān)的問題外,還必須對(duì)振蕩器環(huán)路驅(qū)動(dòng)電平進(jìn)行適當(dāng)量化,以確保在整個(gè)溫度和時(shí)間內(nèi)可接受的產(chǎn)品性能.例如,典型的24 MHz SMT石英晶體的驅(qū)動(dòng)電平規(guī)格最大為100μW.如果石英晶體始終以該極限的某個(gè)倍數(shù)驅(qū)動(dòng),例如200μW;在溫度或時(shí)間上,振蕩器電路可能會(huì)開始永久或間歇地諧振 - 處于石英晶體的寄生或泛音模式.雖然設(shè)計(jì)工程師的清單相對(duì)較低,但是由外部諧振器(例如石英晶體)驅(qū)動(dòng)的皮爾斯振蕩器在典型的產(chǎn)品發(fā)布期間可能是一個(gè)重大挑戰(zhàn).在設(shè)計(jì)階段表征振蕩器回路應(yīng)該是減少產(chǎn)品發(fā)布期間風(fēng)險(xiǎn)以及現(xiàn)場(chǎng)返回的優(yōu)先事項(xiàng).

The Pierce Analyzer System To overcome these challenges and provide an accurate assessment of the oscillator loop dynamics, Abracon’s Advanced Engineering Team has developed a proprietary Pierce Analyzer System (PAS), designed to analyze both the standalone crystal, as well as the performance of that particular crystal in the final circuit.

Key PAS features

• Circuit characterization; provides best possible match between Quartz Crystal, oscillator loop and associated components.

• Eliminates probability of oscillator startup issues related to inadequate design or marginal component performance.

• Eliminates production launch issues related to crystal oscillator based timing circuit.

• Solves for design margin uncertainty.

• Provides customer’s oscillator circuit overview in the form of a detailed report, which could be an ideal 3rd party assessment for the design history file or PPAP documentation. This report encompasses both the stand-alone crystal performance, as well as in-circuit behavior outlining safety factor as a function of crystal’s ESR, etc.

皮爾斯分析儀系統(tǒng)為了克服這些挑戰(zhàn)并提供振蕩器回路動(dòng)態(tài)的準(zhǔn)確評(píng)估,Abracon的高級(jí)工程團(tuán)隊(duì)開發(fā)了專有的皮爾斯分析儀系統(tǒng)(PAS),旨在分析獨(dú)立晶體以及特定晶體的性能晶體在最后的電路中.

關(guān)鍵PAS功能

•電路特性;提供石英晶體,振蕩器環(huán)路和相關(guān)組件之間的最佳匹配.

•消除與設(shè)計(jì)不足或邊緣組件性能相關(guān)的振蕩器啟動(dòng)問題的可能性.

•消除與基于晶體振蕩器的定時(shí)電路相關(guān)的生產(chǎn)啟動(dòng)問題.

•解決設(shè)計(jì)邊際不確定性問題.

•以詳細(xì)報(bào)告的形式提供客戶的振蕩器電路概述,這可能是設(shè)計(jì)歷史文件或PPAP文檔的理想第三方評(píng)估.本報(bào)告既包括獨(dú)立的晶體性能,也包括作為晶體ESR等函數(shù)的安全系數(shù)的在線行為.

Most if not all embedded solutions use the Pierce oscillator configuration,integrated as part of the SoC (systemon-chip). The obvious advantages include cost, size, and power compared to a standalone oscillator. The key limitation is the proper matching of the quartz crystal with the on-board Pierce oscillator.

Figure 1 outlines the oscillator block and the key components that influence the overall performance of the timing loop. Let the effective load capacitance, as seen by the crystal, be CL.

如今,大多數(shù)電子電路(包括微處理器,微控制器,FPGA和CPLD)都基于時(shí)鐘邏輯,需要定時(shí)源. 根據(jù)頻率精度要求,一些采用振蕩器,而另一些采用現(xiàn)成的石英晶體與嵌入大多數(shù)微控制器和微處理器的內(nèi)置振蕩器電路相結(jié)合.

大多數(shù)(如果不是全部)嵌入式解決方案都使用皮爾斯振蕩器配置,作為SoC(systemon-chip)的一部分集成. 與獨(dú)立振蕩器相比,明顯的優(yōu)勢(shì)包括成本,尺寸和功耗. 關(guān)鍵的限制是石英晶振與板載皮爾斯振蕩器的正確匹配.

圖1概述了振蕩器模塊和影響定時(shí)環(huán)路整體性能的關(guān)鍵組件. 讓晶體看到的有效負(fù)載電容為CL.

For example, let C1 = C2 = 27 pF; CIN = 5.0 pF and COUT = 10.0 pF and Board Strays = 0.50 pF.

例如,設(shè)C1 = C2 = 27 pF; CIN = 5.0pF,COUT = 10.0pF,板間距= 0.50pF.

Therefore specifying a crystal with 18.0 pF plating load capacitance would be the closest match for frequency accuracy. The selected capacitors primarily influence the overall oscillator loop capacitance, as seen by the crystal. This effective loop capacitance (CL from Eq. 1) determines how far the oscillator loop is resonating, relative to the desired resonant frequency. However, the overall longterm performance of the oscillator loop is influenced by the following factors:

因此,指定具有18.0 pF電鍍負(fù)載電容的晶體將是頻率精度最接近的匹配. 所選擇的電容主要影響整個(gè)振蕩器環(huán)路電容,如晶體所示. 該有效環(huán)路電容(來自等式1的CL)確定振蕩器環(huán)路相對(duì)于所需諧振頻率諧振的程度. 但是,振蕩器環(huán)路的整體長期性能受以下因素影響:

• The reactive impedance (Xc) of these loop capacitors.

• The inverter amplifier’s transconductance (gm).

• The presence or absence of the current limiting resistor (Rs).

• The presence or absence of the automatic gain control (AGC) or automatic level control (ALC); with-in the integrated oscillator circuit.

These factors collectively set the boundary condition of the design. This boundary condition, commonly referred to as the safety factor (SF), is an important parameter to ensure that the product design has sufficient margin to accommodate part-to-part and lot-to-lot variations; as well as, eliminating product performance uncertainty in production volume. Historically, design engineers have optimized their circuit performance via trial and error, at the expense of sig.

•這些環(huán)路電容器的無功阻抗(Xc).

•逆變器放大器的跨導(dǎo)(gm).

•是否存在限流電阻(Rs).

•是否存在自動(dòng)增益控制(AGC)或自動(dòng)電平控制(ALC); 與集成振蕩器電路配合使用.

這些因素共同設(shè)定了設(shè)計(jì)的邊界條件. 這種邊界條件,通常稱為安全系數(shù)(SF),是確保產(chǎn)品設(shè)計(jì)具有足夠的余量以適應(yīng)零件到零件和批次間差異的重要參數(shù); 以及消除產(chǎn)品性能不確定性的產(chǎn)量. 從歷史上看,設(shè)計(jì)工程師通過試驗(yàn)和錯(cuò)誤優(yōu)化了電路性能,但犧牲了信號(hào).

Fig. 1: The oscillator block and the key components that influence the overall performance of the timing loop.

圖1:振蕩器模塊和影響定時(shí)環(huán)路整體性能的關(guān)鍵部件.

nificant investment in time. Further, to properly determine the oscillator loop dynamics, the most accurate determination is made by breaking the oscillator loop and conducting key measurements using specialized equipment such as a current probe.

及時(shí)投入.此外,為了正確地確定振蕩器環(huán)路動(dòng)態(tài),通過使用諸如電流探頭的專用設(shè)備斷開振蕩器環(huán)路并進(jìn)行關(guān)鍵測(cè)量來進(jìn)行最準(zhǔn)確的確定.

Lastly, these measurements become increasingly sensitive if the timing loop is driven by a tuning-fork (32.768- kHz) crystal. These crystals are extremely sensitive to loading effects and to accurately determine the in-circuit behavior of these components, extreme care and accuracy is essential. For instance, Automotive, medical and consumer electronics solutions typically use tuning fork crystals for their real-time-clocking (RTC) needs. If the selected SOP has limited gain margin, there is a high probability that some percentage of these crystals will not properly start under adverse conditions, such as cold operating temperature (–40°C).

最后,如果定時(shí)環(huán)由音叉(32.768-kHz)晶體驅(qū)動(dòng),則這些測(cè)量變得越來越敏感.這些晶體對(duì)負(fù)載效應(yīng)非常敏感,并且準(zhǔn)確地確定這些元件的在線行為,極其謹(jǐn)慎和準(zhǔn)確性至關(guān)重要.例如,汽車,醫(yī)療和消費(fèi)電子解決方案通常使用音叉晶體來滿足其實(shí)時(shí)時(shí)鐘(RTC)需求.如果所選擇的SOP具有有限的增益裕度,則很可能這些晶體中的某些百分比在不利條件下(例如冷工作溫度(-40℃))不能正常啟動(dòng).

Another example would be a product designed to address the ZigBee related solutions, which typically has a hard boundary condition of ±40 ppm relative to the carrier, for proper operation. This ±40-ppm operational window actually needs to account for

另一個(gè)例子是設(shè)計(jì)用于解決ZigBee相關(guān)解決方案的產(chǎn)品,該解決方案通常具有相對(duì)于載波±40ppm的硬邊界條件,以實(shí)現(xiàn)正確操作.這個(gè)±40 ppm的操作窗口實(shí)際上需要考慮

• Quartz crystal set tolerance.

• Shift through reflow.

• Stability over temperature.

• Aging during product-life-cycle (such as 5 years).

• Frequency pushing and pulling.

If the oscillator loop is not optimized, most of the ±40 ppm can be potentially consumed by the set tolerance of the quartz crystal alone, thereby causing potential field failures.

•石英晶體設(shè)置公差.

•通過回流轉(zhuǎn)換.

•溫度穩(wěn)定性.

•產(chǎn)品生命周期中的老化(例如5年).

•頻率推拉.

如果振蕩器環(huán)路未經(jīng)優(yōu)化,則單獨(dú)使用石英晶體的設(shè)定公差可能會(huì)消耗大部分±40 ppm,從而導(dǎo)致潛在的現(xiàn)場(chǎng)故障.

These frequency domain failures could be primarily attributed to the oscillator frequency drifting over temperature or long-term aging, to the point that the oscillator loop is no longer within the allocated ±40-ppm operational window. Besides the issues related to oscillator-loop accuracy in the frequency domain, the oscillator-loop drive level must also be properly quantified to ensure acceptable product performance over temperature and time. For instance, a typical 24-MHz SMT quartz crystal has a drive level specification of 100 µW max. If the quartz crystal is consistently being driven at some multiple of this limit, such as 200 µW; it is possible that, over temperature or time, the oscillator circuit might start to resonate permanently or intermittently — at a spurious or overtone mode of the quartz crystal. Although relatively low on the checklist of design engineers, the Pierce oscillator driven by an external resonator — such as a quartz crystal — can present a significant challenge during a typical product launch. Characterizing the oscillator loop during the design phase should be a priority to mitigate the risk during product launch as well as field returns down the road.

這些頻域故障主要?dú)w因于振蕩器頻率隨溫度漂移或長期老化,導(dǎo)致振蕩器環(huán)路不再在分配的±40 ppm操作窗口內(nèi).除了與頻域振蕩器環(huán)路精度相關(guān)的問題外,還必須對(duì)振蕩器環(huán)路驅(qū)動(dòng)電平進(jìn)行適當(dāng)量化,以確保在整個(gè)溫度和時(shí)間內(nèi)可接受的產(chǎn)品性能.例如,典型的24 MHz SMT石英晶體的驅(qū)動(dòng)電平規(guī)格最大為100μW.如果石英晶體始終以該極限的某個(gè)倍數(shù)驅(qū)動(dòng),例如200μW;在溫度或時(shí)間上,振蕩器電路可能會(huì)開始永久或間歇地諧振 - 處于石英晶體的寄生或泛音模式.雖然設(shè)計(jì)工程師的清單相對(duì)較低,但是由外部諧振器(例如石英晶體)驅(qū)動(dòng)的皮爾斯振蕩器在典型的產(chǎn)品發(fā)布期間可能是一個(gè)重大挑戰(zhàn).在設(shè)計(jì)階段表征振蕩器回路應(yīng)該是減少產(chǎn)品發(fā)布期間風(fēng)險(xiǎn)以及現(xiàn)場(chǎng)返回的優(yōu)先事項(xiàng).

The Pierce Analyzer System To overcome these challenges and provide an accurate assessment of the oscillator loop dynamics, Abracon’s Advanced Engineering Team has developed a proprietary Pierce Analyzer System (PAS), designed to analyze both the standalone crystal, as well as the performance of that particular crystal in the final circuit.

Key PAS features

• Circuit characterization; provides best possible match between Quartz Crystal, oscillator loop and associated components.

• Eliminates probability of oscillator startup issues related to inadequate design or marginal component performance.

• Eliminates production launch issues related to crystal oscillator based timing circuit.

• Solves for design margin uncertainty.

• Provides customer’s oscillator circuit overview in the form of a detailed report, which could be an ideal 3rd party assessment for the design history file or PPAP documentation. This report encompasses both the stand-alone crystal performance, as well as in-circuit behavior outlining safety factor as a function of crystal’s ESR, etc.

皮爾斯分析儀系統(tǒng)為了克服這些挑戰(zhàn)并提供振蕩器回路動(dòng)態(tài)的準(zhǔn)確評(píng)估,Abracon的高級(jí)工程團(tuán)隊(duì)開發(fā)了專有的皮爾斯分析儀系統(tǒng)(PAS),旨在分析獨(dú)立晶體以及特定晶體的性能晶體在最后的電路中.

關(guān)鍵PAS功能

•電路特性;提供石英晶體,振蕩器環(huán)路和相關(guān)組件之間的最佳匹配.

•消除與設(shè)計(jì)不足或邊緣組件性能相關(guān)的振蕩器啟動(dòng)問題的可能性.

•消除與基于晶體振蕩器的定時(shí)電路相關(guān)的生產(chǎn)啟動(dòng)問題.

•解決設(shè)計(jì)邊際不確定性問題.

•以詳細(xì)報(bào)告的形式提供客戶的振蕩器電路概述,這可能是設(shè)計(jì)歷史文件或PPAP文檔的理想第三方評(píng)估.本報(bào)告既包括獨(dú)立的晶體性能,也包括作為晶體ESR等函數(shù)的安全系數(shù)的在線行為.

正在載入評(píng)論數(shù)據(jù)...

相關(guān)資訊

- [2023-07-12]康納溫菲爾德推出符合Stratum3E...

- [2023-06-26]選擇石英晶體要了解的必要參數(shù),...

- [2023-06-25]艾伯康公司發(fā)布連續(xù)電壓有源晶振...

- [2021-01-18]今日主題:什么樣性能的石英晶振...

- [2021-01-13]是什么原因造成晶振相噪惡化?都...

- [2020-12-09]干貨干貨!愛普生旗下SG-8018系列...

- [2020-09-08]石英Crystal工作原理是怎樣的,這...

- [2020-09-01]Oscillator的制造流程究竟是怎樣...